代码密度增强技术

针对 RISC-V 指令集特性深度优化,通过 Xwingc 扩展指令集、WingGCC 编译器及 WingLib 基础库的全栈协同,显著降低内存占用与芯片成本,实现超越 ARM 的代码密度表现。

技术背景与挑战

RISC-V 的双刃剑

RISC-V 指令集以精简闻名,但在处理相同任务时,相较于 ARM 往往需要执行更多条指令。这种特性导致了代码密度较低,进而要求更大的片上内存(Memory),最终导致芯片成本的增加。

普通 RISC-V

隼瞻方案

通过提高代码密度,显著减少对 Memory 的需求,降低 Memory 面积与成本。

四大技术手段

全栈式优化策略,从指令集到工具链

社区贡献

对 RISC-V 社区的 B 扩展、Zc 扩展、Zicond 等一系列标准扩展提供了有效支持,并进行了进一步优化。

Xwingc 扩展指令集

支持将自主研发的代码密度增强指令 Xwingc 扩展加入到处理器核中。

WingGCC 编译器

解决了 GCC 领域针对性不强的问题。完整匹配各种标准扩展指令和隼瞻自定义扩展指令,同时适配隼瞻专用高效微架构,充分发挥性能。

WingLib 基础库

- 提供标准C库和数学库,专为 code size 和速度优化,优于竞品 5%~20%。

- 提供优化的 DSP 库,结合 DSA 技术,性能达竞品数倍。

- 提供优化的第三方中间件。

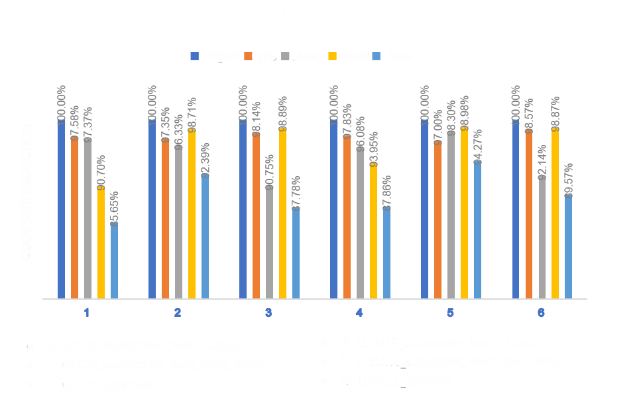

极致的密度优化

我们的优化路径清晰可见。从基础 GCC 出发,叠加 Zc/Zicond 扩展,再引入 Wing 独有的代码密度增强技术,最终实现大幅度的空间节省。

基于 Wing-M130, Wing IDE v1.0, embench 测试案例

代码密度百分比 (数值越小越好)