ArchitStudio 开发平台

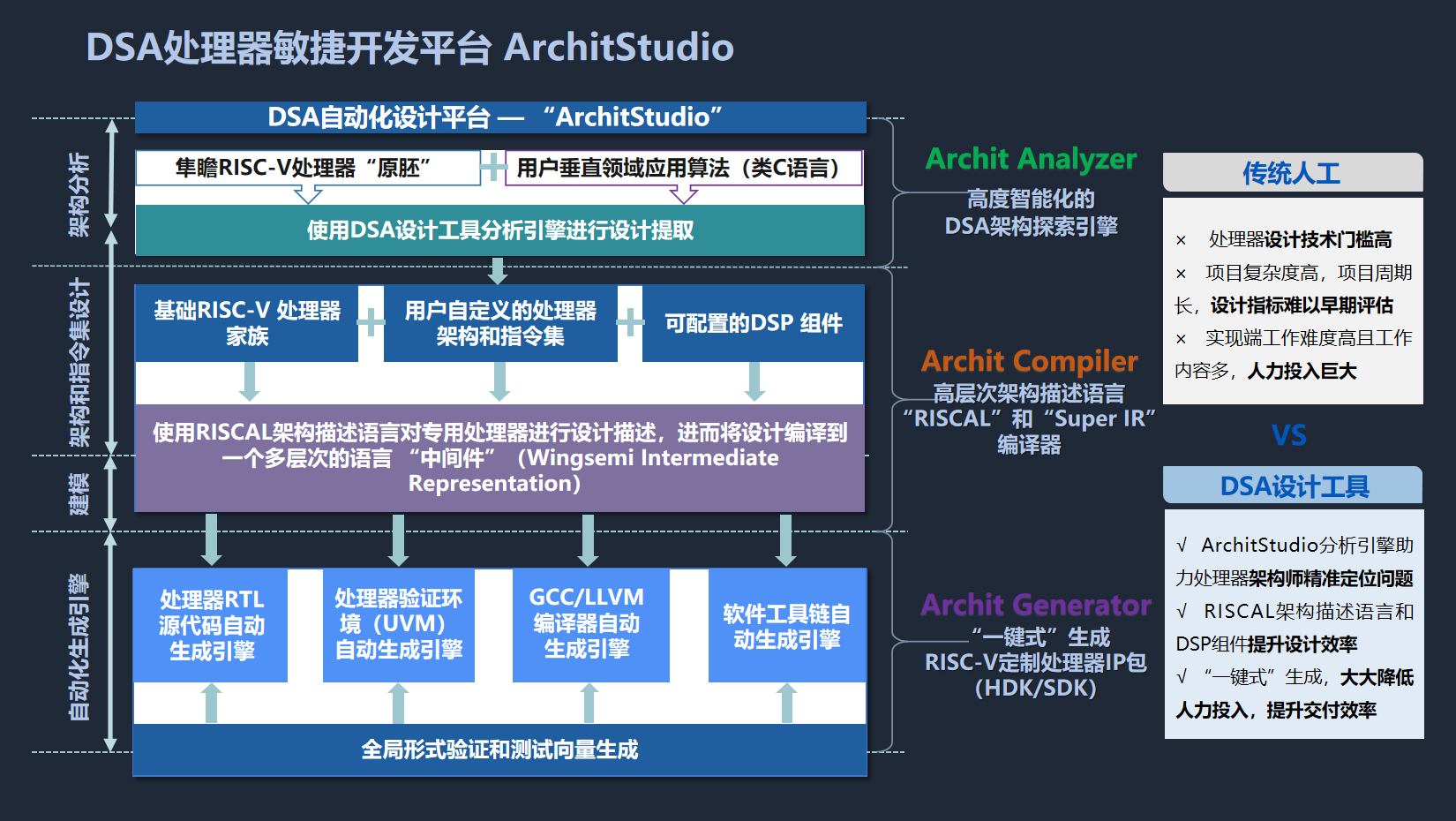

ArchitStudio基于算法芯片化,场景架构化的理念,加速DSA的设计和落地,为以RISC-V定制处理器为核心的SOC设计方法学带来了革命级的改变。在ArchitStudio的基础上,设计人员得以摆脱了RTL级别的繁复开发工作,更专注于架构和指令集的设计;其一键式的SDK生成引擎更是大量减少了软件工具链开发的工作量,显著缩减了处理器开发的人力成本。

2+N 平台战略

以经过验证的基础 IP 为根基,以敏捷开发平台为养料,孕育无限专用处理器生态

RISC-V CPU 基础 IP

精心打磨、充分硅验证的全栈 RISC-V 处理器 IP 家族,是专用处理器设计的“根基”。

ArchitStudio 开发平台

高度自动化的处理器敏捷开发平台,是开发专用处理器的“养料”。

RISC-V for AI

Archit Fusion AI

Wireless

通信连接

Industrial

工业控制

Multimedia

多媒体处理

解决行业痛点:双向奔赴

打破垂直领域与芯片设计之间的壁垒

处理器提供方

- 具备完整的处理器设计能力

- 缺乏对垂直领域的专业理解

ArchitStudio

连接算法与芯片的桥梁

领域专用需求方

- 对场景和算法有深刻认识

- 缺乏处理器设计的专业知识

EDA 辅助的敏捷设计流程

从目标程序到芯片交付,打造全链路闭环

目标程序

Profiler 分析

架构探索

RISCAL 建模

自动生成

Processor Gen

交付包

SDK & HDK

SDK 软件开发包

编译器、调试器、仿真器、性能剖析器

HDK 硬件开发包

RTL 代码、验证环境、综合脚本、FPGA网表

平台核心组件

Architect the Vision, Shape the Future

Archit Analyzer

全方位性能与PPA剖析

从架构、微架构层面提供不同维度的详细信息,为架构优化指明方向。

- 指令 Trace & 函数调用关系分析

- 流水线分析 & 指令利用率分析

Archit Compiler

所见即所得的设计模式

将繁琐的底层代码编写转变为“乐高”式的积木搭建,降低开发门槛。

- Core Editor: 可视化核心配置

- RISCAL Editor: 辅助指令集设计

Archit Generator

全栈工具链一键生成

基于 RISCAL 指令描述和 WingIR 多层次语言中间表达,自动生成全套开发环境。

- Compiler, Simulator, Profiler 生成

- RTL, Verification, Libraries 生成

方法学

用户价值

为何选择 ArchitStudio 进行 DSA 设计?

极致的 DSA 性能

通过专用指令集设计,大幅提升 PPA 指标。

大幅降低门槛

让更多工程师参与并主导 DSA 处理器设计。

显著缩短周期

从架构定义到 IP 包交付时间压缩数倍。

提升设计质量

自动化流程减少人为错误,确保一致性。

早期精准评估

智能探索引擎助力更早、更准确地评估PPA设计指标。

聚焦核心创新

设计师得以从繁重的底层实现中解放,专注于最具价值的架构创新和算法优化。

拥抱RISC-V生态

基于开放、活力的RISC-V指令集,确保处理器的灵活性和生态兼容性。